#### **SIEMENS EDA**

# ODB++ Inside for Cadence® Allegro®

Release vNPI 2305 May 2023

#### Unpublished work. © 2023 Siemens

This Documentation contains trade secrets or otherwise confidential information owned by Siemens Industry Software Inc. or its affiliates (collectively, "Siemens"), or its licensors. Access to and use of this Documentation is strictly limited as set forth in Customer's applicable agreement(s) with Siemens. This Documentation may not be copied, distributed, or otherwise disclosed by Customer without the express written permission of Siemens, and may not be used in any way not expressly authorized by Siemens.

This Documentation is for information and instruction purposes. Siemens reserves the right to make changes in specifications and other information contained in this Documentation without prior notice, and the reader should, in all cases, consult Siemens to determine whether any changes have been made.

No representation or other affirmation of fact contained in this Documentation shall be deemed to be a warranty or give rise to any liability of Siemens whatsoever.

If you have a signed license agreement with Siemens for the product with which this Documentation will be used, your use of this Documentation is subject to the scope of license and the software protection and security provisions of that agreement. If you do not have such a signed license agreement, your use is subject to the Siemens Universal Customer Agreement, which may be viewed at <a href="https://www.sw.siemens.com/en-US/sw-terms/base/uca/">https://www.sw.siemens.com/en-US/sw-terms/base/uca/</a>, as supplemented by the product specific terms which may be viewed at <a href="https://www.sw.siemens.com/en-US/sw-terms/supplements/">https://www.sw.siemens.com/en-US/sw-terms/supplements/</a>.

SIEMENS MAKES NO WARRANTY OF ANY KIND WITH REGARD TO THIS DOCUMENTATION INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, AND NON-INFRINGEMENT OF INTELLECTUAL PROPERTY. SIEMENS SHALL NOT BE LIABLE FOR ANY DIRECT, INDIRECT, INCIDENTAL, CONSEQUENTIAL OR PUNITIVE DAMAGES, LOST DATA OR PROFITS, EVEN IF SUCH DAMAGES WERE FORESEEABLE, ARISING OUT OF OR RELATED TO THIS DOCUMENTATION OR THE INFORMATION CONTAINED IN IT, EVEN IF SIEMENS HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES.

TRADEMARKS: The trademarks, logos, and service marks (collectively, "Marks") used herein are the property of Siemens or other parties. No one is permitted to use these Marks without the prior written consent of Siemens or the owner of the Marks, as applicable. The use herein of third party Marks is not an attempt to indicate Siemens as a source of a product, but is intended to indicate a product from, or associated with, a particular third party. A list of Siemens' Marks may be viewed at: <a href="https://www.plm.automation.siemens.com/global/en/legal/trademarks.html">www.plm.automation.siemens.com/global/en/legal/trademarks.html</a>. The registered trademark Linux<sup>®</sup> is used pursuant to a sublicense from LMI, the exclusive licensee of Linus Torvalds, owner of the mark on a world-wide basis.

#### **About Siemens Digital Industries Software**

Siemens Digital Industries Software is a global leader in the growing field of product lifecycle management (PLM), manufacturing operations management (MOM), and electronic design automation (EDA) software, hardware, and services. Siemens works with more than 100,000 customers, leading the digitalization of their planning and manufacturing processes. At Siemens Digital Industries Software, we blur the boundaries between industry domains by integrating the virtual and physical, hardware and software, design and manufacturing worlds. With the rapid pace of innovation, digitalization is no longer tomorrow's idea. We take what the future promises tomorrow and make it real for our customers today. Where today meets tomorrow. Our culture encourages creativity, welcomes fresh thinking and focuses on growth, so our people, our business, and our customers can achieve their full potential.

Support Center: support.sw.siemens.com

Send Feedback on Documentation: support.sw.siemens.com/doc\_feedback\_form

# **Table of Contents**

| Chapter 1 ODB++Design Export                                | 5 |

|-------------------------------------------------------------|---|

|                                                             |   |

|                                                             | 6 |

|                                                             | 7 |

|                                                             | 9 |

| ODB++ Inside Wizard Pages                                   |   |

| Specifying File Options and Output Options Page             |   |

| Specifying Partial Export Parameters Page                   |   |

| Specifying Additional Parameters Pages                      | 9 |

| Chapter 2                                                   |   |

| System Administrator Notes                                  | 3 |

|                                                             |   |

| Running the Translator from Design Workbench                |   |

| ODB++Design Entity Naming Rules                             |   |

| ODB++ Inside Environment Variables                          |   |

| Configuration Parameters                                    |   |

| Command Line Parameters                                     |   |

| Thermal Model Configuration                                 |   |

| Structure of the Thermal Model File                         |   |

| Thermal Model Examples                                      |   |

| Information Acquired from Cadence Allegro Data              |   |

| Generated Extract Files. 5                                  |   |

| Importing Allegro Geometry Properties                       |   |

| Importing Allegro Component Properties                      |   |

| Deriving Component Outline From Specific Subclasses         |   |

| Cadence Allegro DFA Table                                   |   |

| Supported Features                                          |   |

| Support for Improved Component Placement                    |   |

| Support for Mask Layers Associated With Inner Copper Layers |   |

| Support for Padstack Types and Usage                        |   |

| Support for Test Point Shapes                               |   |

| Support for Intentional Shorts. 7                           |   |

| Support for Components Excluded From BOM                    |   |

| Support for DFA Boundaries                                  |   |

| Support for Partial ODB++Design Output                      |   |

| Support for Flex Subtypes                                   |   |

| Support for Boundary Elements                               |   |

| Support for Backdrill Size 7                                |   |

| Support for Dielectric Layer Subtypes                       |   |

| Support for Bend Areas                                      |   |

| Support for Skipping Extraction of Net Impedance Average 8  |   |

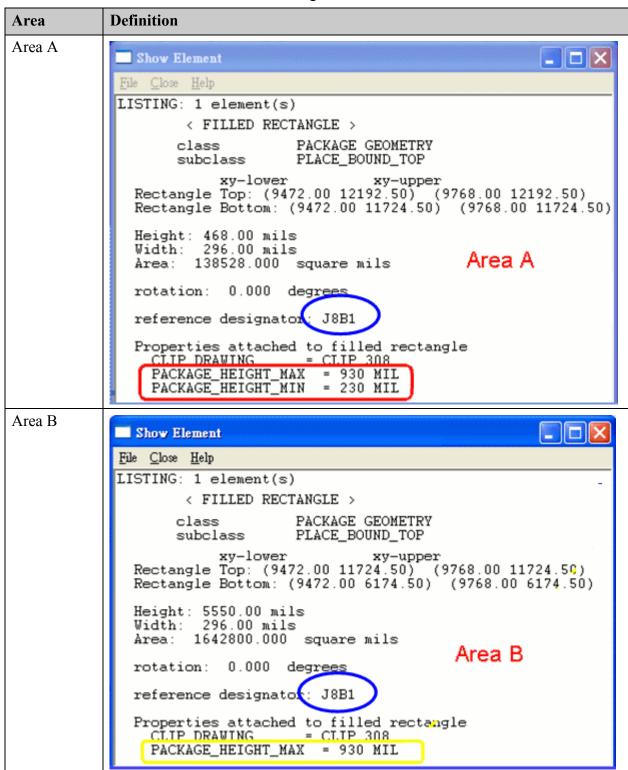

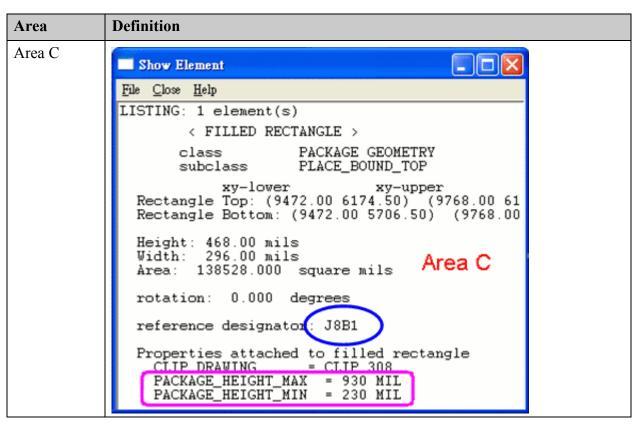

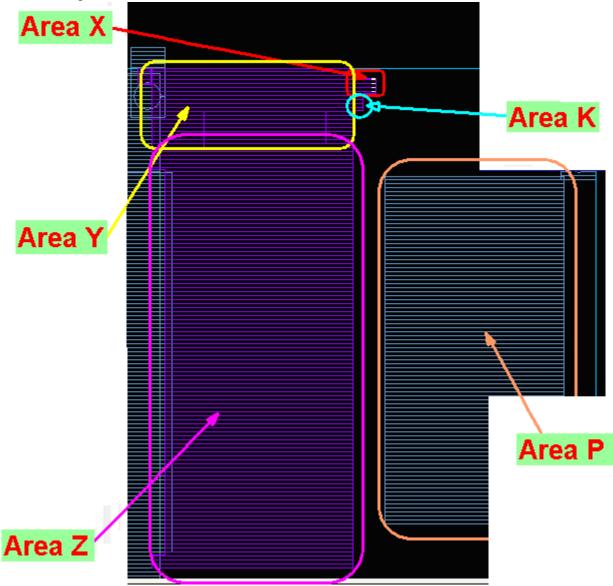

| Package Height Properties                                   | 0 |

#### **Table of Contents**

| Support for CLASS CONSTRAINT REGION            | 88 |

|------------------------------------------------|----|

| Support for Translating Back-Drill Information | 88 |

| Support for Mirrored Padstacks                 | 88 |

| Support for the COMPONENT KEEPOUT Class        | 88 |

# Chapter 1 ODB++Design Export

ODB++Design format can capture all CAD or EDA assembly and PCB fabrication information in a single, unified file structure. ODB++ Inside is installed as part of Cadence Allegro to allow you to export a design to ODB++Design and to view the resulting ODB++ product model.

ODB++ Inside for Cadence Allegro contains the following components:

- **BRD2ODB translator** Converts .out files, generated by Cadence Allegro, to ODB++Design version 8 or ODB++ version 7. The name of the Cadence Allegro design is contained in the names of the .out files. See "Generated Extract Files" on page 55.

- o If you are running the translator from within Cadence Allegro, you can specify a .brd file as the input path.

- o If you are running ODB++ Inside stand-alone, you must specify a directory containing the .out files that have been extracted from Cadence Allegro.

- **ODB++** Viewer Displays the resulting ODB++Design information, graphically. See *ODB++* Viewer User Guide.

When Allegro is to be launched from the Allegro Design Workbench, environment variable PCBDW\_USER\_PATH must be set when ODB++ Inside is installed, as described in "Running the Translator from Design Workbench" on page 34.

The translator supports files from version 11 through 17.2 of these Cadence Allegro products:

- .*brd* file From Cadence Allegro PCB Designer

- .mcm file From Cadence Allegro Package Designer (APD)

- .sip file From Cadence SIP

The translator does not include the option to save as the earlier ODB++ Version 6. This functionality was removed so that there is no confusion over what should be sent to manufacturing. Manufacturers must use a software version capable of reading ODB++ Version 7 or ODB++Design Version 8 format. Mentor Graphics Frontline applications such as Genesis work with a variation of the ODB++Design format, but they can import and use the ODB++ Version 7 and the ODB++Design Version 8 format.

| Translating a Design to ODB++Design Format | 6  |

|--------------------------------------------|----|

| Saving the Configuration                   | 7  |

| Editing the Matrix File                    | 9  |

| ODB++ Inside Wizard Pages                  | 12 |

# Translating a Design to ODB++Design Format

You use the ODB++ Inside for Cadence Allegro translator to specify parameters and to run the translation, to export a Cadence Allegro design to an ODB++ product model.

#### **Prerequisites**

- Environment variables have been set. See "ODB++ Inside Environment Variables" on page 35.

- Configuration parameters have been set. See "Configuration Parameters" on page 36.

- Thermal models have been configured. See "Thermal Model Configuration" on page 49.

#### **Procedure**

- 1. Launch ODB++ Inside from within Cadence Allegro or stand-alone:

- From within Cadence Allegro, choose File > Export > ODB++ Inside or click

- Use a line mode command to activate the stand-alone translator:

- o Windows:

```

"%ALLEGRO BRD2ODB%/brd2odb.exe" -gui

```

o UNIX:

```

$ALLEGRO BRD2ODB/brd2odb -qui

```

See "Command Line Parameters" on page 43.

- 2. Specify the information described in "Specifying File Options and Output Options Page" on page 13.

- If you are running ODB++ Inside from within Cadence Allegro, you can specify a .*brd* file as the input path.

- If you are running ODB++ Inside stand-alone, you must specify a directory containing the .out files that have been extracted from Cadence Allegro. See "Generated Extract Files" on page 55.

- 3. If you have selected Export Option = Partial, specify the partial export parameters as described in "Specifying Partial Export Parameters Page" on page 17.

- 4. If you have selected Show more options = Yes, specify the information as described in "Specifying Additional Parameters Pages" on page 19.

- 5. Click **Next** on the last page of parameters to perform the translation.

- 6. If you want to restart the wizard and re-enter the options, click **Setting > Reset Wizard**.

#### Results

The product model is written in ODB++Design format to the specified location.

If you have selected Open ODB++ viewer = Yes, the ODB++ Inside wizard pauses and prompts you to verify the creation of the job. Click **Close** to exit the application:

ODB++ Viewer opens, displaying the product model as described in *ODB++ Viewer User Guide*.

# **Saving the Configuration**

If you will be using the same configuration parameters for several translations, you can save the configuration to a file.

You can save the configuration to the standard user location, to the standard system location, or to another location. The user-level configuration, if it exists, is loaded when ODB++ Inside starts. Otherwise, the system-level configuration is used to supply default values for the wizard.

#### **Prerequisites**

Run the ODB++ Inside wizard as described in "Translating a Design to ODB++Design Format" on page 6.

#### **Procedure**

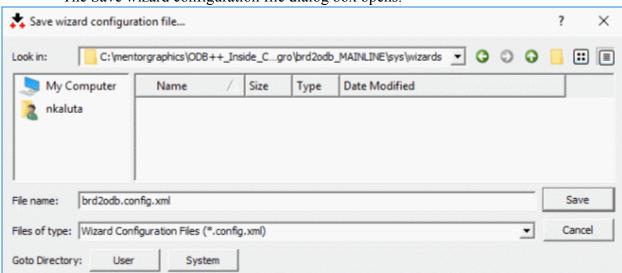

1. Choose **Setting > Save Config**.

The Save wizard configuration file dialog box opens.

#### 2. Specify the parameter values:

| Parameter | Description                                                                                                                                                                                                                     |

|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Look in:  | The directory in which to save the configuration file. This can be the standard user location or the standard system location, or another location.                                                                             |

|           | • To store files at the user location, click the <b>User</b> button. The user location is displayed in this field.                                                                                                              |

|           | If there is a file saved at the user location, it is loaded when ODB++ Inside opens.                                                                                                                                            |

|           | • To store the file at the system location, click the <b>System</b> button. The system location is displayed in this field.                                                                                                     |

|           | This configuration is loaded when ODB++ Inside opens, if there is no configuration file in the user location.                                                                                                                   |

|           | • You can save the configuration file in another location. To use the parameter settings, copy the file to the standard name, in either the user location or the system location, before opening ODB++ Inside.                  |

| File name | The file name to which to save the configuration.                                                                                                                                                                               |

|           | If you are storing the file at the user location or at the system location, and you want the wizard to load the default values from this file on startup, save the configuration to the standard file name: brd2odb.config.xml. |

|           | If you are storing the configuration at a different location, to a file that will be copied to the user location or the system location as needed, you can specify any file name.                                               |

| Parameter     | Description                                                                                              |

|---------------|----------------------------------------------------------------------------------------------------------|

| Files of type | If you are storing the file at the user location or at the system location, leave the default file type. |

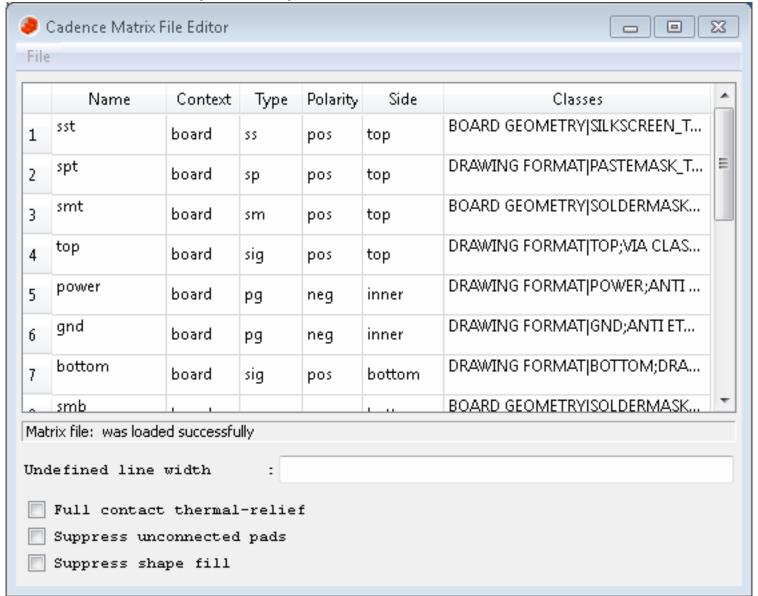

## **Editing the Matrix File**

If necessary, you can edit the information about the layers that were extracted from the Cadence Allegro design. For each layer you can edit the context, type, polarity, and side.

The options of the matrix file editor are equivalent to the options on the Artwork Control Form dialog box of Cadence Allegro.

Layers are translated according to the data taken from the files *layers\_<product\_model>.out* and *films\_<product\_model>.out*. It is not unusual to find data for copper layers mixed with document layers.

The translator designates the top and bottom layers according to the pairs of class | sub-class ETCH|<*layer\_name*>. If several layers contain these pairs, the first one found is used. To avoid the mixing and duplication of layer data, it is necessary to edit the matrix file before translation.

The first time a design is translated, it does not usually contain a matrix file.

#### **Procedure**

1. Use the drop-down lists in the Cadence Matrix File Editor window to edit parameters so that each layer is correctly defined.

- If you change a top or bottom layer to a document layer, its name is changed to what it was originally.

- If you change a document layer to a signal layer, its name is assigned according to the ETCH sub-class found in it.

Make sure that changes to layers remain synchronized. For example, signal must be assigned side = top or bottom and power and ground layers must be side = inner. They cannot be of context misc. Document layers must be assigned side = auto and polarity = pos. Unsynchronized data causes incorrect translation.

2. Set options for thermal relief, unconnected pads, and shape fill for each layer.

| Option                       | Explanation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Full contact thermal-        | Controls the creation of thermal symbols on a specific layer.                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| relief                       | • selected — Suppresses the creation of thermal symbols.                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|                              | • cleared — Creates thermal symbols, if they are defined, in this way:                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|                              | • If there are <i><thermal name="" symbol="">.outdra</thermal></i> files, thermal symbols are added as defined in these files.                                                                                                                                                                                                                                                                                                                                                                                       |

|                              | • If there are no <i>outdra</i> files, and Use thermal model file = Use file was specified in the wizard, the thermal model specified in Set filename of thermal model is searched. If there are thermal symbols defined there, they are added.                                                                                                                                                                                                                                                                      |

|                              | The file <i>valor_ex.il</i> creates ASCII files named <i><thermal name="" symbol="">.outdra</thermal></i> if there are DRA files with the design. These files are used to create thermal symbols. Each file defines one thermal symbol. Only the thermals for which there are <i>outdra</i> files are replaced.                                                                                                                                                                                                      |

| Suppress<br>unconnected pads | Controls whether unconnected pads are suppressed for the selected layer.                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Suppress shape fill          | Controls the creation of the laminate area for the selected layer during translation.                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                              | <ul> <li>selected — Creation of the laminate area is suppressed. The design<br/>must have filled areas replaced with separation lines in Power &amp;<br/>Ground layers.</li> </ul>                                                                                                                                                                                                                                                                                                                                   |

|                              | • cleared — By default, text on P&G layers is translated with negative polarity. This reads product models in the same way the -s switch is used in the Allegro Artwork command. The laminate area is created for all negative layers by creating a single surface consisting of the board outline (filled) with all split plane areas subtracted from it. Creation of the laminate area in ODB++ is equivalent to the "shapefill" algorithm in Allegro (the -s switch is used to suppress the shapefill algorithm). |

3. Choose **File > Save** to save the corrections. You can specify the edited matrix file in Matrix file so that the translation creates layers according to the file.

# **ODB++ Inside Wizard Pages**

The ODB++ Inside wizard comprises a set of pages that lead you through the translation stages: setting the file options and output options, configuring partial output, setting additional translation parameters, and running the translation.

The pages are listed in order of execution of the wizard stages:

| Specifying File Options and Output Options Page | 13 |

|-------------------------------------------------|----|

| Specifying Partial Export Parameters Page       | 17 |

| Specifying Additional Parameters Pages          | 19 |

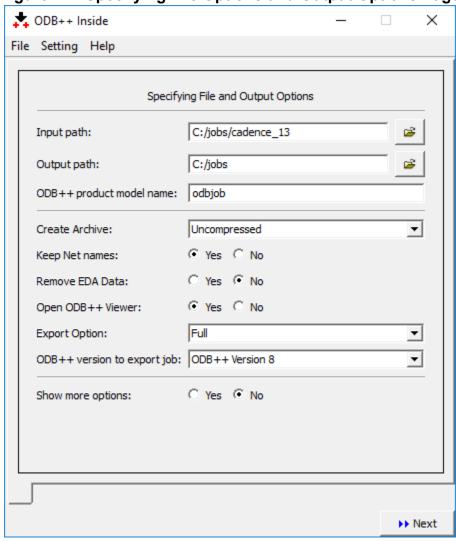

# **Specifying File Options and Output Options Page**

You access this page while performing Step 2 of the procedure "Translating a Design to ODB++Design Format".

You must provide input and output paths and output options needed by the translator, and select actions to be performed by the translator.

Figure 1-1. Specifying File Options and Output Options Page

#### **Objects**

**Table 1-1. File Options**

| Object                    | Description                                                                                                                                                                                                                                                              |

|---------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Input path                | The input path of the Allegro design.                                                                                                                                                                                                                                    |

|                           | Click to browse to a file or a directory.                                                                                                                                                                                                                                |

|                           | If you are running ODB++ Inside from within Cadence Allegro, you can specify a <i>.brd</i> file as the input path. If you are running ODB++ Inside stand-alone, you must specify a directory containing <i>.out</i> files that have been extracted from Cadence Allegro. |

|                           | See "Generated Extract Files" on page 55.                                                                                                                                                                                                                                |

| Output path               | The path for the ODB++Design output.                                                                                                                                                                                                                                     |

|                           | Click to browse to a file or a directory.                                                                                                                                                                                                                                |

| Output product model name | The name of the ODB++Design product model to be created.                                                                                                                                                                                                                 |

**Table 1-2. Translator Actions**

| Field              | Description                                                                                            |

|--------------------|--------------------------------------------------------------------------------------------------------|

| Create<br>Archive  | Controls the format of the ODB++Design output.                                                         |

|                    | Uncompressed (default)                                                                                 |

|                    | • Tar — Compresses the ODB++Design folders into a tared file.                                          |

|                    | • <b>Tar gzip (.tgz)</b> — Compresses the ODB++Design folders into a tared and zipped <i>tgz</i> file. |

| Keep Net names     | Controls whether net names are renamed numerically or are kept as their original names.                |

| Remove EDA<br>Data | Removes component/package data.                                                                        |

**Table 1-2. Translator Actions (cont.)**

| Field                | Description                                                                                                                                                                                                                                                                                            |

|----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Open ODB++<br>Viewer | Opens the ODB++ Viewer application to display the imported design, when the translation completes. The ODB++ Inside wizard remains open, but is paused.  The wizard displays the message Verify the creation of the job. Click                                                                         |

|                      | Close to exit the application.                                                                                                                                                                                                                                                                         |

|                      | <b>II</b> Wiz − □ ×                                                                                                                                                                                                                                                                                    |

|                      | Stage 1 of 1.  Verify the creation of the job. Press Close to exit the application.  Close  The ODB++ Viewer opens, displaying the resulting ODB++Design data.                                                                                                                                         |

|                      | To close ODB++ Viewer opens, displaying the resulting ODB++Design data.  To close ODB++ Viewer and the ODB++ Inside wizard, perform one of these tasks:                                                                                                                                                |

|                      | • Choose <b>File &gt; Exit</b> to close the ODB++ Viewer.                                                                                                                                                                                                                                              |

|                      | • In the Wizard Paused message box, click Close.                                                                                                                                                                                                                                                       |

|                      | If your examination of the ODB++Design data indicates that you need to change import parameters, you can click <b>Setting &gt; Reset Wizard</b> in the ODB++ Inside wizard to restart the wizard. If you have saved your configuration, you only need to enter the parameters that need to be changed. |

|                      | See <i>ODB++ Viewer User Guide</i> .                                                                                                                                                                                                                                                                   |

**Table 1-2. Translator Actions (cont.)**

| Field             | Description                                                                                                                               |

|-------------------|-------------------------------------------------------------------------------------------------------------------------------------------|

| Export Option     | Controls how much data is exported to ODB++Design:                                                                                        |

|                   | • Full — All information in the design Export Fabrication.                                                                                |

|                   | Partial — You can select which data is exported. See "Specifying"                                                                         |

|                   | Partial Export Parameters Page" on page 17.                                                                                               |

|                   | • <b>FAB</b> — Exports layers and data options for fabrication:                                                                           |

|                   | Physical nets - output for net points                                                                                                     |

|                   | Outer copper layers                                                                                                                       |

|                   | Silk Screen layers                                                                                                                        |

|                   | Solder Paste layers                                                                                                                       |

|                   | Solder Mask layers                                                                                                                        |

|                   | Drill / Rout layers                                                                                                                       |

|                   | Document layers                                                                                                                           |

|                   | Inner layers                                                                                                                              |

|                   | • <b>ASSY</b> — Exports layers and data options for assembly:                                                                             |

|                   | <ul> <li>Components/Packages &amp; Logical nets - components + logical nets<br/>(net nodes/net attributes/net properties)</li> </ul>      |

|                   | Physical nets - output for net points                                                                                                     |

|                   | Outer copper layers                                                                                                                       |

|                   | Silk Screen layers                                                                                                                        |

|                   | Solder Paste layers                                                                                                                       |

|                   | Solder Mask layers                                                                                                                        |

|                   | Drill / Rout layers                                                                                                                       |

|                   | Document layers                                                                                                                           |

| ODB++Desig        | One of these ODB++Design versions:                                                                                                        |

| n version to      | ODB++Design Version 8                                                                                                                     |

| export job        | • ODB++ Version 7                                                                                                                         |

| Show more options | Activates the options for setting additional parameters as described in Table 1-3 through Table 1-6.                                      |

| Next              | Does one of the following:                                                                                                                |

| ▶ Next            | • If you selected <b>Export Option</b> = <b>Partial</b> , displays Specifying Partial Export Parameters Page.                             |

|                   | <ul> <li>If you selected Export Option ≠ Partial AND Show more options = Yes, displays Specifying Additional Parameters Pages.</li> </ul> |

|                   | <ul> <li>If you selected Export Option ≠ Partial AND Show more options = No, runs the translation.</li> </ul>                             |

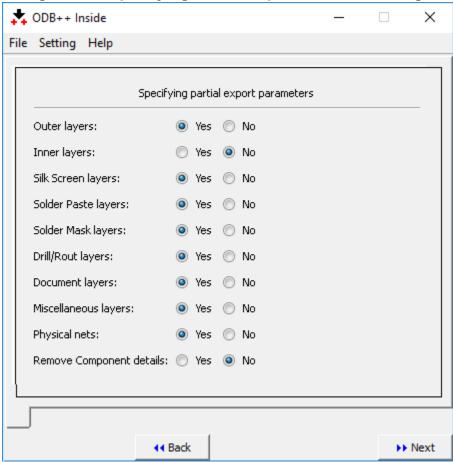

### **Specifying Partial Export Parameters Page**

You access this page while performing Step 3 of the procedure "Translating a Design to ODB++ Format".

You can specify which information should be extracted from the design.

Figure 1-2. Specifying Partial Export Parameters Page

#### **Objects**

| Object                | Description                                                                    |

|-----------------------|--------------------------------------------------------------------------------|

| Outer layers          | Yes / No                                                                       |

|                       | Controls whether to include the outer layers in the ODB++ product model.       |

| Inner layers          | Yes / No                                                                       |

|                       | Controls whether to include the inner layers in the ODB++ product model        |

| Silk Screen<br>layers | Yes / No                                                                       |

|                       | Controls whether to include the silk screen layers in the ODB++ product model. |

| Object                 | Description                                                                                                    |

|------------------------|----------------------------------------------------------------------------------------------------------------|

| Solder Paste<br>layers | Yes / No                                                                                                       |

|                        | Controls whether to include the solder paste layers in the ODB++ product model.                                |

| Solder Mask            | Yes / No                                                                                                       |

| layers                 | Controls whether to include the solder mask layers in the ODB++ product model.                                 |

| Drill/Rout             | Yes / No                                                                                                       |

| layers                 | Controls whether to include the drill/rout layers in the ODB++ product model.                                  |

| Document               | Yes / No                                                                                                       |

| layers                 | Controls whether to include the document layers in the ODB++ product model.                                    |

| Physical nets          | Yes / No                                                                                                       |

|                        | Controls whether to include the net names in the ODB++ product model.                                          |

| Miscellaneous          | Yes / No                                                                                                       |

| layers                 | Controls whether to include the miscellaneous layers in the ODB++ product model.                               |

| Remove                 | Yes / No                                                                                                       |

| component<br>details   | Controls whether to exclude attributes and properties of the components from the ODB++ product model.          |

| Back                   | Displays the Specifying File Options and Output Options Page.                                                  |

| <b>44</b> Back         |                                                                                                                |

| Next                   | Does one of the following:                                                                                     |

| <b>▶</b> Next          | • If you selected <b>Show more options</b> = <b>Yes</b> , displays the Specifying Additional Parameters Pages. |

|                        | • If you selected <b>Show more options</b> = <b>No</b> , runs the translation.                                 |

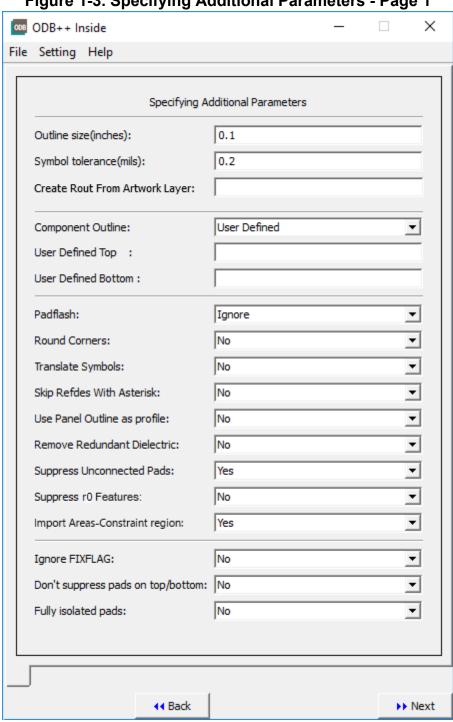

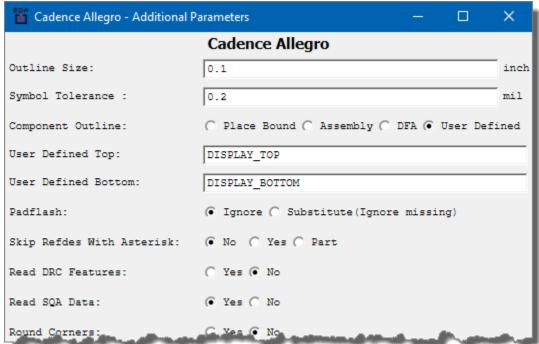

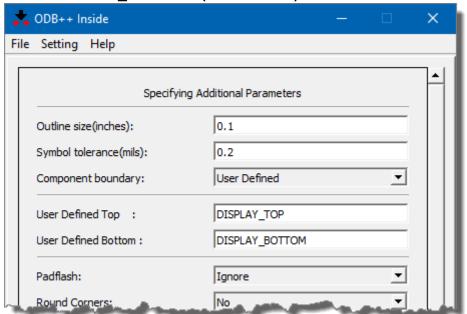

# **Specifying Additional Parameters Pages**

You access these pages while performing Step 4 of the procedure "Translating a Design to ODB++ Format."

You can specify additional and configuration parameters.

Figure 1-3. Specifying Additional Parameters - Page 1

ODB++ Inside File Setting Help Specifying Additional Parameters Delete Extracted Files: ○ Yes No Import Keepin/out regions: No Read SQA Data: No ▾ Yes Read \$NONE\$ net: ▾ Œ AIF file Ä Matrix file: Open Matrix file Editor **∢∢** Back ▶ Next

Figure 1-4. Specifying Additional Parameters - Page 2

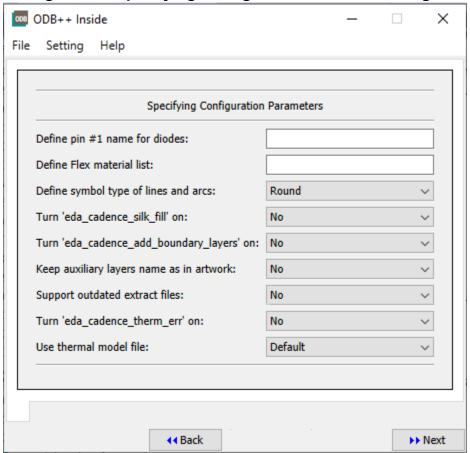

Figure 1-5. Specifying Configuration Parameters Page

#### **Objects**

Table 1-3. Specifying Additional Parameters - Page 1

| Object                | Description                                                                                                                                                                                                                                                                                                                                                                                          |

|-----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Outline size (inches) | When creating negative plane layers, the size of the frame is the value of this parameter. For accurate translation this value should match the -o option in the Cadence Allegro artwork program. If these two parameters differ, the frame will be created according to the value in Outline size. The value is in inches.  The field allows a precision of up to four digits. For example, 0.4321. |

Table 1-3. Specifying Additional Parameters - Page 1 (cont.)

| Object                  | Description                                                                                                                                                                                                                                         |

|-------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Symbol tolerance (mils) | The system compares shapes that are input, with symbols previously input in the same session, and with standard and semi-standard system symbols.                                                                                                   |

|                         | • 0 — only if the input shape exactly matches a system symbol, is the system symbol used. If it does not match, the input shape is used "as is" without change.                                                                                     |

|                         | • positive value — the input shape is compared to system symbols within the tolerance specified. If it can be matched, the system symbol is used.                                                                                                   |

|                         | Use this parameter as appropriate for the type of file you expect to input. The lower the tolerance the more critical the system is in judging that shapes are equivalent. The value is specified in mils.                                          |

|                         | The field allows a precision of up to four digits. For example, 0.2134.                                                                                                                                                                             |

| Create Rout From        | Controls how the rout is created:                                                                                                                                                                                                                   |

| Artwork Layer           | • If the field contains the name of a valid layer, as specified in the Allegro artwork, the features in that layer are used to create an ODB++ rout layer with the original name.                                                                   |

|                         | • If this field is empty, or contains the name of a non-existing layer, the translation creates a rout layer named "profile" by merging the features from the following Allegro artwork CLASS/SUBCLASS in the <i>geoms_</i> < <i>pm</i> >.out file: |

|                         | • If DESIGN_OUTLINE data exists (Allegro 17.2 or later):                                                                                                                                                                                            |

|                         | BOARD GEOMETRY:DESIGN_OUTLINE"&"BOARD GEOMETRY:CUTOUT                                                                                                                                                                                               |

|                         | • If DESIGN_OUTLINE data does not exist (older versions):                                                                                                                                                                                           |

|                         | BOARD GEOMETRY:OUTLINE"&"BOARD<br>GEOMETRY:CUTOUT                                                                                                                                                                                                   |

|                         | Related line mode command switch is -ral. See "Command Line Parameters" on page 43.                                                                                                                                                                 |

Table 1-3. Specifying Additional Parameters - Page 1 (cont.)

| Object              | Description                                                                                                                                                                                                                                                                                                                                                                                       |

|---------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Component Outline   | Controls how the component outline is created.                                                                                                                                                                                                                                                                                                                                                    |

|                     | • Placebound — (Recommended) When place bound shapes are available (PART GEOMETRY sub-classes PLACE_BOUND_TOP and PLACE_BOUND_BOTTOM) they are used for the component outline. Otherwise, the limits of the assembly features are used.                                                                                                                                                           |

|                     | • Assembly— The limits of the assembly features are used. A heuristic algorithm attempts to determine the actual component outline from the collection of data on the sub-classes ASSEMBLY_TOP and ASSEMBLY_BOTTOM of the package geometry. This may result in an unexpected component outline if the data defining it is not complete in terms of ODB++, that is, a well defined closed polygon. |

|                     | • <b>DFA</b> — If DFA boundaries data exists, the component outline is taken from the PART GEOMETRY sub-classes DFA_BOUND_TOP and DFA_BOUND_BOTTOM. Otherwise, pin bounding boxes are used.                                                                                                                                                                                                       |

|                     | • User Defined — The component outline is taken from the sub-<br>classes entered into User Defined Top and User Defined Bottom.                                                                                                                                                                                                                                                                   |

| User Defined Top    | Available only when Component Outline = User Defined.                                                                                                                                                                                                                                                                                                                                             |

| User Defined Bottom | Specify the top and bottom subclasses from which the component outline is taken.                                                                                                                                                                                                                                                                                                                  |

|                     | These fields must be set with the values specified in the component subclasses file. See "Deriving Component Outline From Specific Subclasses" on page 69.                                                                                                                                                                                                                                        |

Table 1-3. Specifying Additional Parameters - Page 1 (cont.)

| Object            | Description                                                                                                                                                                                                                                                                                                                                                                  |

|-------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Padflash          | Allegro pad definitions can have padflash codes that override the pad size information for the padstack. This information is extracted into the twelfth field of the pad extract file (pads_<br>brd name>.out).                                                                                                                                                              |

|                   | For instance, on fiducials, a designer defines a padstack called FID120RD40RD that appears in Allegro as a 120 mil diameter pad with a 120 mil diameter solder mask. It also has a padflash definition of RD40.                                                                                                                                                              |

|                   | • <b>Ignore</b> — (default) The Padflash field is ignored and instead, the pad size is used. In the example, the example padstack would be constructed of 120 mil diameter pads during EDA translation.                                                                                                                                                                      |

|                   | • Substitute (Ignore missing) — (recommended) Sets the Padflash definition using the following method:                                                                                                                                                                                                                                                                       |

|                   | • If the Padflash code exists and the <i>thermal_models</i> file using Cadence Allegro padflashes exists, the name in the PADFLASH field is used in conjunction with the thermal models file to determine what is placed at the location. In the example, the PADFLASH name RD40 would determine the actual fiducial on the copper layer based on the current thermal model. |

|                   | <ul> <li>In other cases, the configuration parameters     eda_cadence_read_dra and eda_cadence_therm_err control the     translator behavior:</li> </ul>                                                                                                                                                                                                                     |

|                   | eda_cadence_read_dra = yes — The file <thermal name="" symbol="">.outdra is read (if exists) during translation, providing the PADFLASH symbol definition.</thermal>                                                                                                                                                                                                         |

|                   | eda_cadence_read_dra = no — The file <thermal name="" symbol=""> .outdra is ignored.</thermal>                                                                                                                                                                                                                                                                               |

|                   | eda_cadence_therm_err = no — If the Padflash does not exist in the <i>thermal_models</i> file or as an <i>outdra</i> file, the original pad size is used.                                                                                                                                                                                                                    |

|                   | eda_cadence_therm_err = yes — If the Padflash does not exist in the <i>thermal_models</i> file or as <i>outdra</i> file, the translation fails with a message listing the padstack name.                                                                                                                                                                                     |

| Round Corners     | Indicates whether corners should be rounded.                                                                                                                                                                                                                                                                                                                                 |

|                   | • No — (default) process precise (square) corners.                                                                                                                                                                                                                                                                                                                           |

|                   | • Yes — round corners of polygons (contours).                                                                                                                                                                                                                                                                                                                                |

| Translate Symbols | Indicates whether symbols should be translated as components.                                                                                                                                                                                                                                                                                                                |

|                   | <ul> <li>Yes — (default) symbols are translated as components. If there are multiple shapes, each will be translated as a separate component.</li> <li>No — symbols are not translated.</li> </ul>                                                                                                                                                                           |

Table 1-3. Specifying Additional Parameters - Page 1 (cont.)

| Object                         | Description                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|--------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Skip Refdes With<br>Asterisk   | Controls whether components with names containing an asterisk (*) should be translated.                                                                                                                                                                                                                                                                                                                                                               |

|                                | • No — All components are translated. (default)                                                                                                                                                                                                                                                                                                                                                                                                       |

|                                | • Yes — Components with names containing an asterisk are not translated.                                                                                                                                                                                                                                                                                                                                                                              |

|                                | • Part — The translation excludes components whose RefDes contains an asterisk (*) but includes their pad and drill features.                                                                                                                                                                                                                                                                                                                         |

| Use Panel Outline as profile   | Controls which data with CLASS = BOARD GEOMETRY in the <i>geoms_<pm>.out</pm></i> file is used to define the step profile:                                                                                                                                                                                                                                                                                                                            |

|                                | <ul> <li>Yes — Step profile is taken from one of the following subclasses, in this order of priority: <ul> <li>a. PANEL_OUTLINE</li> <li>b. DESIGN_OUTLINE</li> <li>c. OUTLINE</li> </ul> </li> <li>No — Step profile is taken from one of the following subclasses, in this order: <ul> <li>a. DESIGN_OUTLINE</li> <li>b. OUTLINE</li> </ul> </li> <li>Related line mode command switch is -up. See "Command Line Parameters" on page 43.</li> </ul> |

| Remove Redundant<br>Dielectric | Controls whether successive dielectric layers are combined:  • No — (default) Combines successive dielectric layers.                                                                                                                                                                                                                                                                                                                                  |

|                                | • Yes — Does not combine successive dielectric layers, which may result in the wrong calculation of back drill spans.                                                                                                                                                                                                                                                                                                                                 |

|                                | Related line mode command switch is -rrd. See "Command Line Parameters" on page 43.                                                                                                                                                                                                                                                                                                                                                                   |

Table 1-3. Specifying Additional Parameters - Page 1 (cont.)

| Object                             | Description                                                                                                                                                                                |

|------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Suppress<br>Unconnected Pads       | Controls whether unconnected pads are included in the translated design if the Allegro design contains the following:                                                                      |

|                                    | • In the films file, SUPPRESS_UNCONNECTED_PADS = Yes.                                                                                                                                      |

|                                    | • In the pads extract file, FIXFLAG = o (optional). If FIXFLAG = f (fixed), it can be ignored by selecting Ignore FIXFLAG.                                                                 |

|                                    | This sets configuration parameter eda_cadence_suppress.                                                                                                                                    |

|                                    | Pads on negative layers and pads associated with embedded components are never suppressed.                                                                                                 |

|                                    | • Yes — Unconnected pads are not translated. This option activates the advanced suppressing options listed in Table 1-4.                                                                   |

|                                    | • No (default) — Unconnected pads are translated.                                                                                                                                          |

|                                    | Related line mode command switches are -iff, -bb, -fi, and -ups. See "Command Line Parameters" on page 43.                                                                                 |

| Suppress r0 Features               | Controls whether to suppress the creation of r0 lines and arcs on copper and solder layers.                                                                                                |

| Import Areas-<br>Constraint region | When set to Yes, triggers the generation of a single ODB++ product model layer by the name of "fab_drc." The layer is generated based on the Allegro layer group called Constraint region. |

|                                    | Related line mode command switch is -rr. See "Command Line Parameters" on page 43.                                                                                                         |

| Back                               | Does one of the following:                                                                                                                                                                 |

| <b>44</b> Back                     | • If you selected <b>Export Option</b> = <b>Partial</b> , displays the Specifying Partial Export Parameters Page.                                                                          |

|                                    | <ul> <li>If you selected Export Option ≠ Partial, displays the Specifying<br/>File Options and Output Options Page.</li> </ul>                                                             |

| Next                               | Displays Page 2 of Specifying Additional Parameters. See Table 1-5.                                                                                                                        |

| <b>▶▶</b> Next                     |                                                                                                                                                                                            |

**Table 1-4. Specifying Additional Parameters - Suppress Unconnected Pads**

| Object                                                                                                                                                                                                                             | Description                                              |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------|

| Prerequisite: Suppress Unconnected Pads = Yes (See Table 1-3)                                                                                                                                                                      |                                                          |

| Note: The following options are available to control which pads are suppressed, unless you are using options in Cadence Allegro V16.2 to control how to treat unconnected pads, and you access the translator from within Allegro. |                                                          |

| Ignore FIXFLAG                                                                                                                                                                                                                     | Ignores the setting of FIXFLAG in the pads extract file. |

Table 1-4. Specifying Additional Parameters - Suppress Unconnected Pads

| Object                            | Description                                                                                                                                                                                          |

|-----------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Don"t suppress pads on top/bottom | Controls whether unconnected pads at the top and bottom of a drill are suppressed. Available only if Suppress Unconnected Pads = Yes.                                                                |

|                                   | Yes — Unconnected pads at the top and bottom of a drill are not suppressed. (All unconnected pads other than those on the top and bottom of a drill are suppressed)                                  |

|                                   |                                                                                                                                                                                                      |

|                                   | <ul> <li>No (default) — Unconnected pads at the top and bottom of a drill are suppressed. (All unconnected pads other than those on the top and bottom layers of a board are suppressed.)</li> </ul> |

|                                   | TH blind buried                                                                                                                                                                                      |

**Table 1-4. Specifying Additional Parameters - Suppress Unconnected Pads**

| Object              | Description                                                                                                                                                                                                                                                                                                            |

|---------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Fully isolated pads | Controls which pads are considered to be unconnected. Available only if Suppress Unconnected Pads = Yes.                                                                                                                                                                                                               |

|                     | • Yes — Only single pads, touching no other feature on the layer, are considered to be unconnected.                                                                                                                                                                                                                    |

|                     | Fully isolated                                                                                                                                                                                                                                                                                                         |

|                     | <ul> <li>No — (default) All of these pads are considered to be unconnected:</li> <li>A single totally isolated pad.</li> <li>Two pads touching or intersecting.</li> <li>A pad transversed by a trace not through its center.</li> <li>A pad touching a surface where its center is not inside the surface.</li> </ul> |

|                     | Fully isolated  Touching or intersecting                                                                                                                                                                                                                                                                               |

|                     | Transversed, but not through the center  Touching a surface, with the center outside the surface                                                                                                                                                                                                                       |

Table 1-5. Specifying Additional Parameters - Page 2

| Object                    | Description                                                                                                                                   |

|---------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|

| Delete Extracted<br>Files | Controls whether temporary extract files created during translation are deleted.                                                              |

| Import Keepin/out regions | When set to Yes, triggers the generation of multiple DRC layers beginning with the prefix "drc_".                                             |

|                           | <ul> <li>Allegro layers Route keepout, Route keepin and Via keepout are<br/>used to generate an ODB++ layer called drc_route.</li> </ul>      |

|                           | • Allegro layers Package keepout, Package keepin, Component keepout and Component keepin are used to create drc_comp_top and drc_comp_bottom. |

|                           | • Allegro layers No_Probe_Top and No_Probe_Bottom are used to create drc_tp_top and drc_tp_bottom.                                            |

Table 1-5. Specifying Additional Parameters - Page 2 (cont.)

| Object            | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|-------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

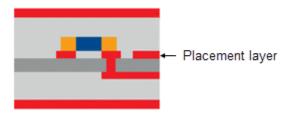

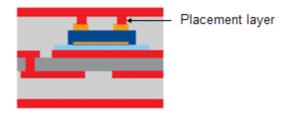

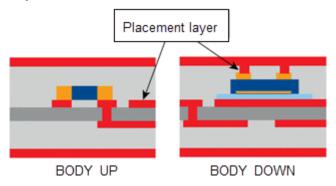

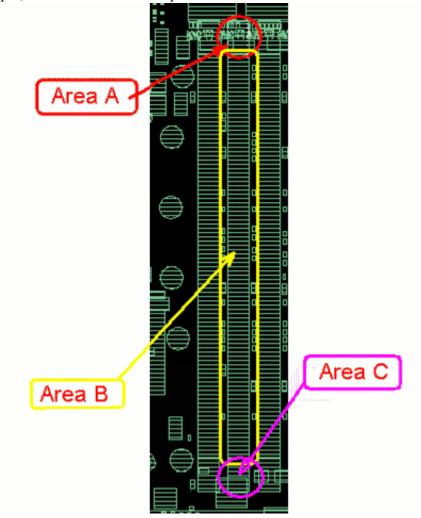

| Read SQA Data     | <ul> <li>Controls whether Signal Quality Analysis data should be read.</li> <li>Yes — SQA data is read and a signal quality layer is created.</li> <li>No — A signal quality data layer is not created and the tech file is not read. The translation takes less time.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |